# **Keystone Enclave** An Open-Source Secure Enclave for RISC-V

**Dayeol Lee<sup>1,2</sup>**, David Kohlbrenner, Kevin Cheang<sup>1</sup>, Cameron Rasmussen<sup>1</sup>, Kevin Laeufer<sup>1</sup>, Ian Fang, Akash Khosla, Chia-Che Tsai<sup>2</sup>, Sanjit Seshia<sup>1</sup>, Dawn Song<sup>2,3</sup>, and Krste Asanovic<sup>1,2</sup>

University of California, Berkeley \*

Collaborators: Ilia Lebedev<sup>4</sup>, and Srinivas Devadas<sup>4</sup>

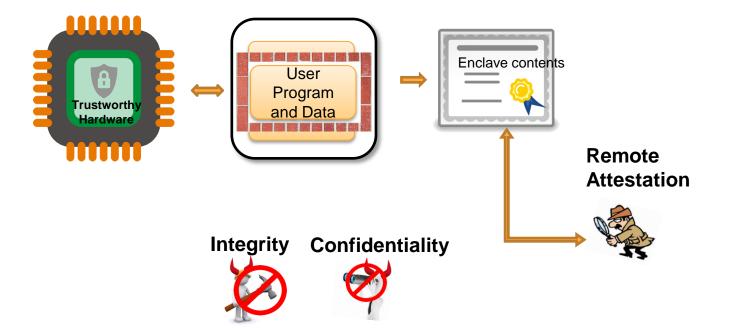

#### What is a Secure Enclave?

#### **Secure Enclave as a Cornerstone Security Primitive**

- Strong security capabilities

- Authenticate itself (device)

- Authenticate software

- Guarantee the integrity and privacy of remote execution

- A cornerstone for building new security applications

- Confidential computing in the cloud (e.g., machine learning)

- Secure IoT sensor network

### Why do we need an Open-Source Enclave?

- Existing enclave systems are proprietary and difficult to experiment with

- Closed-source commercial hardware (e.g., Intel SGX, ARM TrustZone)

- Lack of good research infrastructure

- A Lot of Challenges for Enclaves

- Hardware vulnerabilities: Intel SGX ForeShadow (USENIX'18), AMD SEV SEVered (EuroSec'18)

- Side channel attacks and physical attacks

- Important questions: do patches really fix the problem? Are there any other issues?

#### **Open Source Design**

- Provides transparency & enables high assurance

- Builds a community to help people work on the same problems

# **Keystone Enclave**

#### **Keystone: Open Framework for Secure Enclaves**

- The First Full-Stack Open-Source Enclave for Minimal Requirements

- Root of trust, security monitor, device driver, SDK, .... Ο

- Memory isolation, secure bootstrapping, remote attestation, .... Ο

- Isolation only with Standard RISC-V Primitives

- RISC-V Privileged ISA (U-, S-, and M-mode support) Ο

- Physical Memory Protection (PMP) Ο

- Demonstrate in unmodified processors Ο

- Open Framework: Built Modular & Portable for Easy Extension

- Platform-agnostic isolated execution environment Ο

- Platform-speci Ο

- github.com/keystone-enclave Use various er Ο

#### **Earlier Work: Sanctum**

- The First Enclave Design in RISC-V ISA

- V. Costan et al., USENIX Security '16

- Proof of concept in C++ (<u>https://github.com/pwnall/sanctum</u>)

- Non-standard Hardware Extension

- PMP was introduced in 2017 (RISC-V Priv. v1.10)

- Keystone and Sanctum

- Keystone was built from scratch

- Keystone shares many good practices from prior experiences of Sanctum

- The primary goal of Keystone is to make an open end-to-end framework

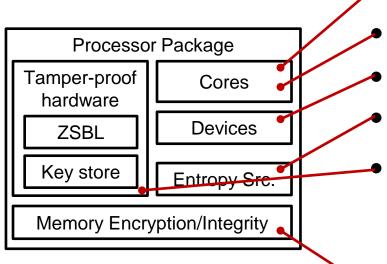

#### What Hardware Do We Need?

- RISC-V Physical Memory Protection (PMP)

- RISC-V U-, S-, and M-mode

- (RISC-V) Device Gasket PMP (i.e., iopmp)

- An Entropy Source available at boot

- Root of Trust (preferably a crypto engine)

- Measuring & signing the security monitor

- Platform key store

- If untrusted/external DRAM –

memory encryption/integrity engine

(not implemented yet)

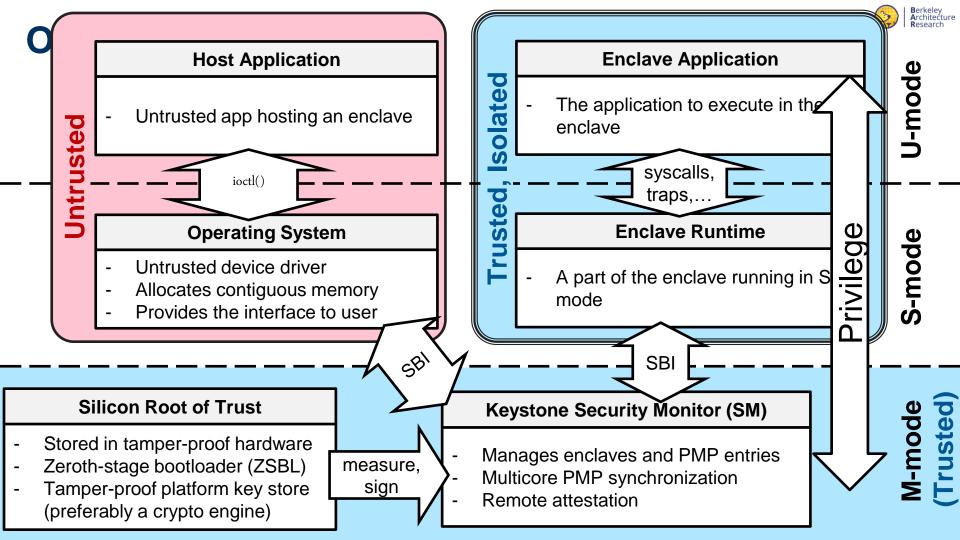

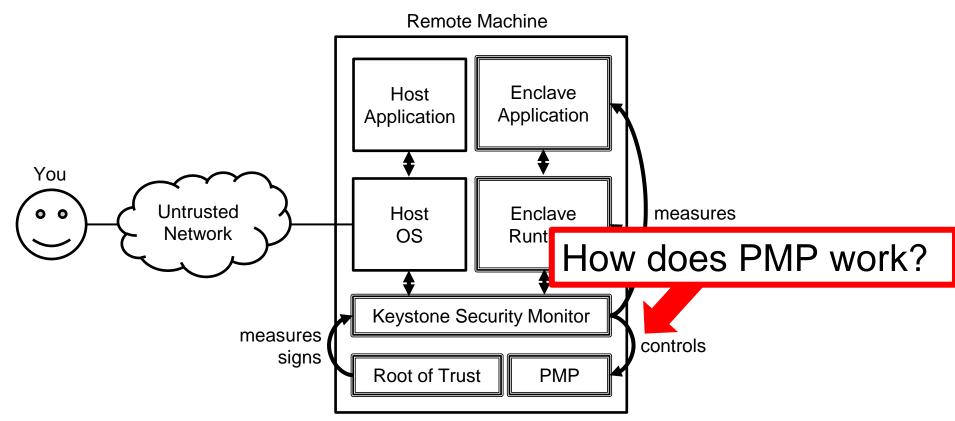

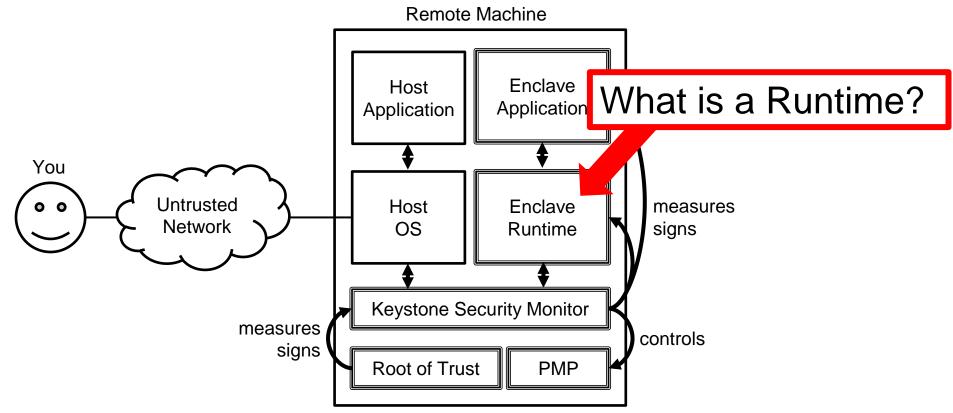

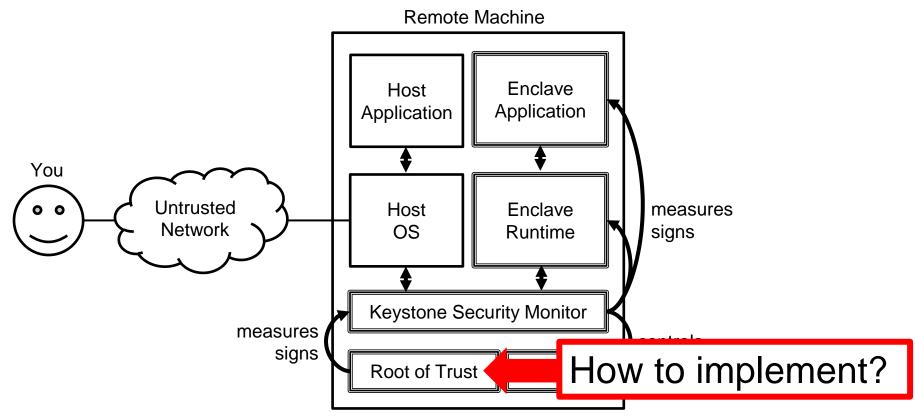

#### **Keystone Overview (Simplified)**

#### **Keystone Overview (Simplified)**

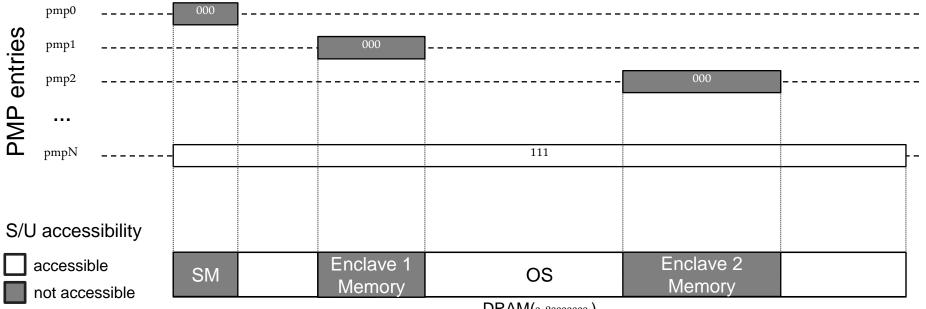

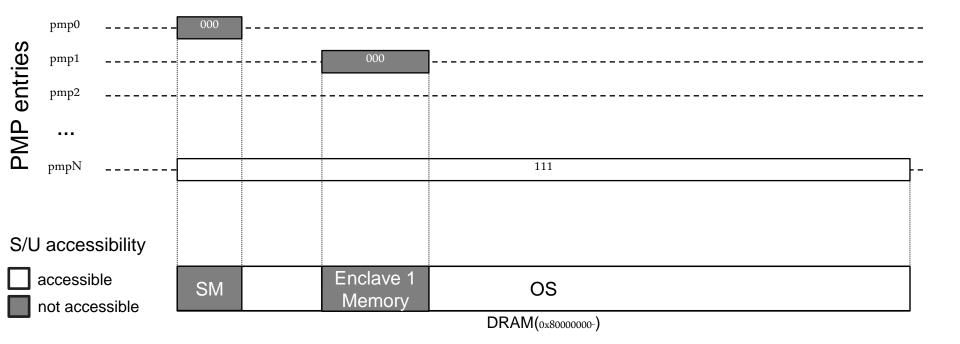

### Memory Isolation with RISC-V PMP

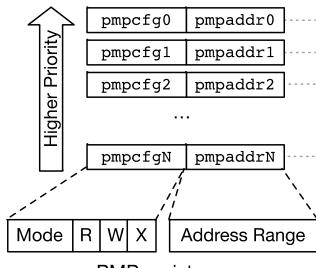

- Physical Memory Protection (PMP)

- Special registers to control permissions of U- and S-mode accesses to a specified memory region

- # of PMP entries can vary (e.g., default Rocket has 8)

- Statically prioritized by the order of entry indices

- O Whitelist-based

- O Dynamically configurable by M-mode

- Addressing modes: NAPOT (>= 4-bytes), Base/Bound

- How Keystone uses PMP

- Top/bottom PMP entries are reserved for SM/OS

- 1 PMP entry for each "active" enclave

- NAPOT > 4KB (fragmentation / Linux buddy allocation)

PMP registers

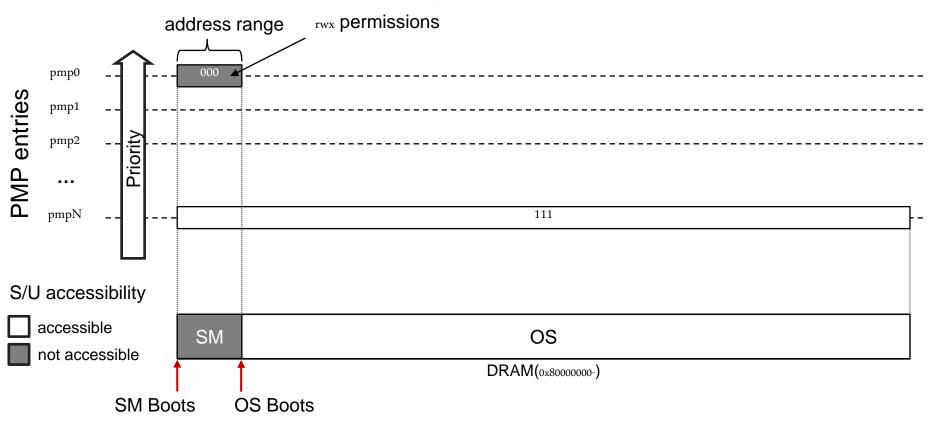

#### **Isolation via Switching PMP Permission Bits**

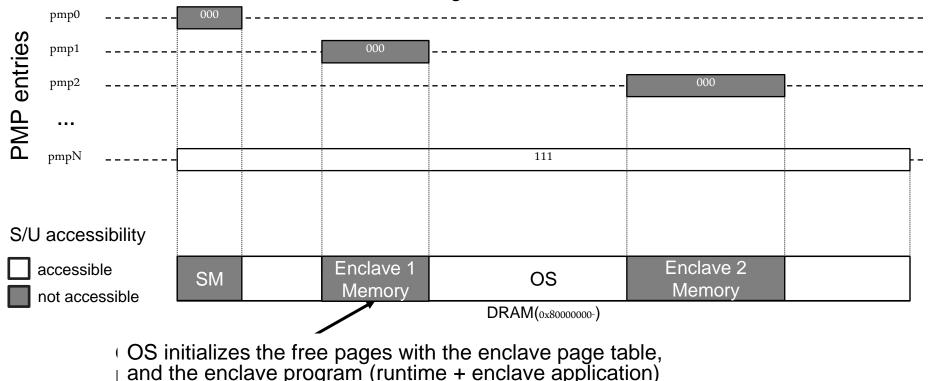

#### **Creating an Isolated Enclave**

SM sets PMP entry; OS can ask SM to create as many enclaves as the number of remaining PMP entries

14 | and the

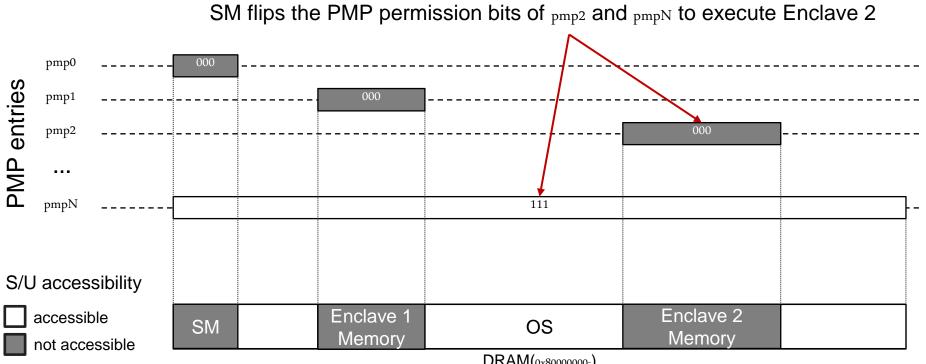

#### **Executing an Enclave**

DRAM(0x8000000-)

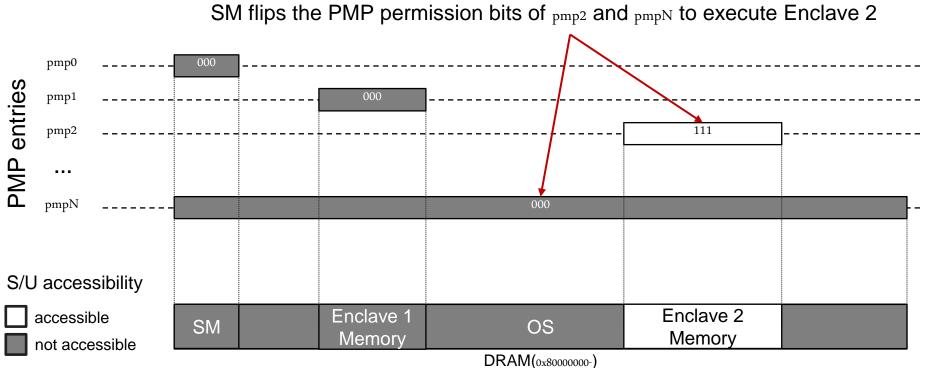

#### **Executing an Enclave**

DRAM(0x8000000-)

#### **Executing an Enclave**

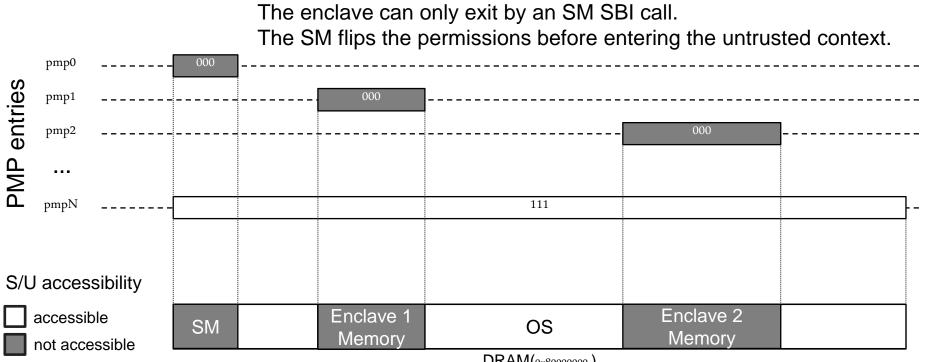

#### (Asynchronous) Exit and Resume

DRAM(0x8000000-)

#### **Destroying an Enclave**

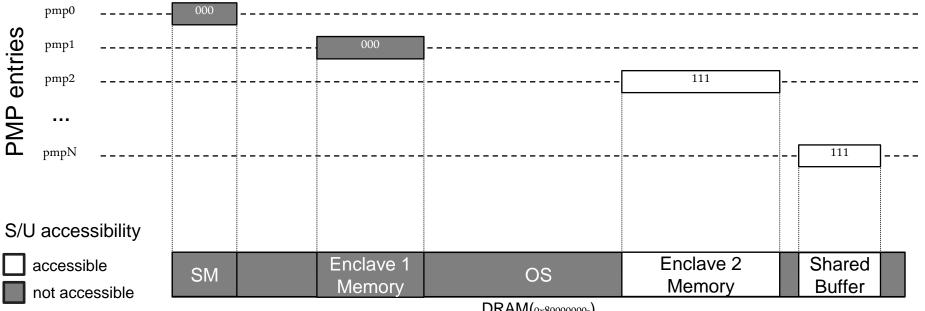

#### **Untrusted Shared Buffer**

The OS can allocate a shared buffer in OS memory The SM uses the last PMP entry to allow the enclave to access the buffer.

#### **Keystone Overview Revisited**

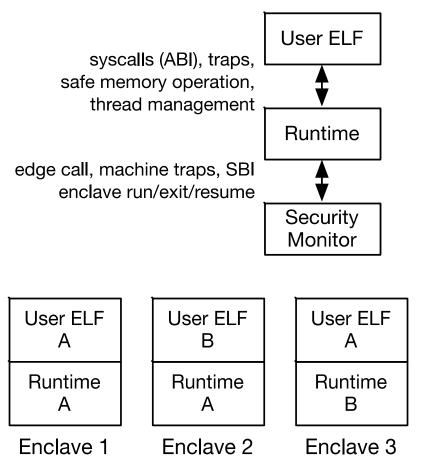

### **S-Mode Enclave Runtime**

- Provides Kernel-like Functionality

- o Syscalls, traps

- o thread and page table management

- Useful Layer of Abstraction

- Least privilege of U-mode code

- Additional functionality without complicating the SM

- $\circ$  SM < 2K LoC + 5K LoC crypto lib.

- Reusability

- Compatible with multiple user programs

- Can act as a shield system

(e.g., Haven, Graphene) in SGX

#### **Keystone Overview Revisited**

#### **Silicon Root of Trust**

- Tamper-proof hardware that cryptographically hashes the security monitor, provisions an attestation key, and signs them with device's secret key.

- Various ways to implement the root of trust

- Various entropy sources, various platform key store, and implementation of the crypto engine

- Keystone uses Sanctum's root of trust which uses ECDSA and SHA-3

4:30pm - 5:00pm30 minsInfo (i)Secure RISC-VSecure Bootstrapping of Trusted Software in RISC-V

Ilia Lebedev - Graduate Student, Massachusetts Institute of Technology

#### **Keystone Overview Revisited**

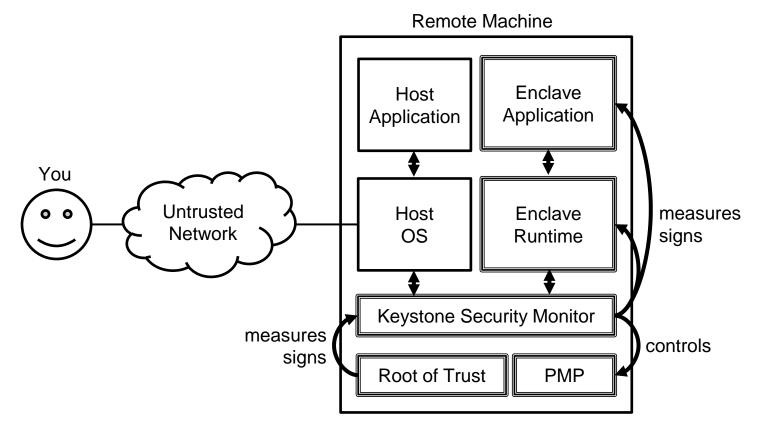

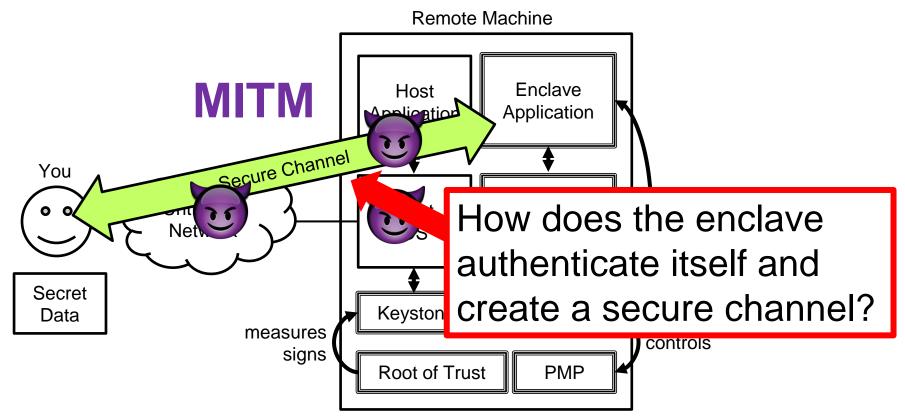

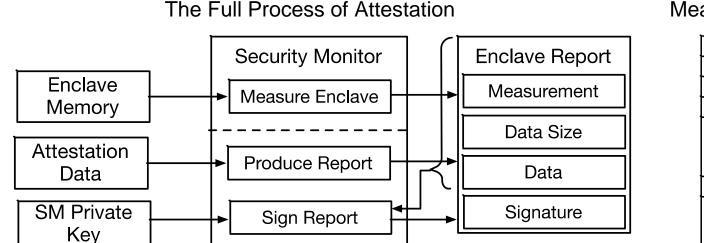

#### **Remote Attestation**

- SM measures the enclave upon enclave creation

- Enclave may bind a key to the enclave report

- SM signs the enclave report and hands it (+ SM report) to the user

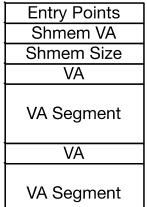

Measurement Layout

#### **Project Status**

- Testable in Various Platforms

- Latest RISC-V QEMU: functionality test, development

- Latest FireSim (v1.4.0): performance analysis, hardware modification

- SiFive Unleashed: runs on a real quadcore in-order processor!

- Ongoing Efforts

- Formal verification of PMP-based security monitor

- Mitigating cache side-channel attacks using platform features

- Contributions Needed!

- Building software stack: more use cases, libraries, edge compiler, ...

- Adding software/hardware extensions

e.g., demand paging, memory encryption/integrity, multithreading, CMA integration, ...

### **Project Links**

• Deployment:

Ο

0

- QEMU:

- FireSim:

- SiFive Unleashed:

- Keystone Repository:

- Keystone-SDK: https://github.com/keystone-enclave/keystone-sdk

- Device Driver: <u>https://github.com/keystone-enclave/riscv-linux</u>

- Security Monitor: <u>https://github.com/keystone-enclave/riscv-pk</u>

- A Simple Runtime: <u>https://github.com/keystone-enclave/keystone-runtime</u>

- Demo:

https://github.com/keystone-enclave/keystone-demo

https://github.com/keystone-enclave/keystone

https://github.com/keystone-enclave/keystone-firesim

https://github.com/keystone-enclave/keystone-hifive-unleashed

- Documentation (more coming):

- Website/Blog: <u>https://keystone-enclave.org</u>

- Development Docs: <u>https://docs.keystone-enclave.org</u>

## Demo

libsodium

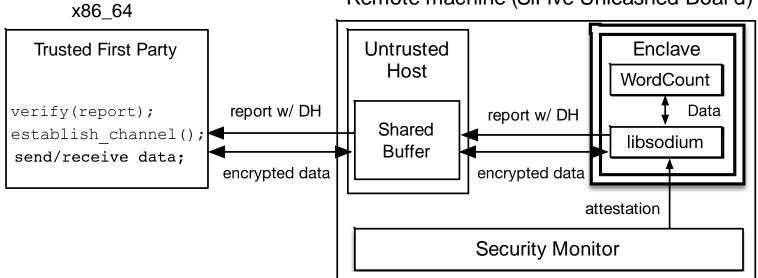

#### **A Remote Enclave with Secure Channel**

- SiFive Unleashed board + simulated non-standard hardware

- Root of trust: Modified FU540 FSBL with hard-coded device key

- Successfully ported libsodium for ECDH Key Exchange

Remote machine (SiFive Unleashed Board)

#### Conclusion

Architecture

- Runs on standard RISC-V cores

- Modular design for better extensibility & portability

- Use Cases

- Secure hardware research (e.g., LLC side-channel defense w/ way partitioning + PMP)

- Building secure systems (e.g., Secure IoT network)

- Opens up Research Opportunities around Hardware Security

- Formal Verification of PMP and Security Monitor Implementation

- Performance Analysis

- Defending Side Channels & Physical Attacks

- Multi-level Security (MLS) for Sensitive Data Analytics

## **Thank You!**

Dayeol Lee (<u>dayeol@Berkeley.edu</u>) David Kohlbrenner (<u>dkohlbre@berkeley.edu</u>) Forum (<u>keystone-enclave@googlegroups.com</u>)