# The RISC-V Instruction Set Manual: Volume II

Privileged Architecture

Version 20241101

# **Table of Contents**

| Pr | reamble                                                                  | I  |

|----|--------------------------------------------------------------------------|----|

| Pr | reface                                                                   | 2  |

| 1. | Introduction                                                             | 9  |

|    | 1.1. RISC-V Privileged Software Stack Terminology                        | 9  |

|    | 1.2. Privilege Levels                                                    | 10 |

|    | 1.3. Debug Mode                                                          | 11 |

| 2. | Control and Status Registers (CSRs)                                      | 12 |

|    | 2.1. CSR Address Mapping Conventions                                     | 12 |

|    | 2.2. CSR Listing                                                         | 13 |

|    | 2.3. CSR Field Specifications                                            | 20 |

|    | 2.3.1. Reserved Writes Preserve Values, Reads Ignore Values (WPRI)       | 20 |

|    | 2.3.2. Write/Read Only Legal Values (WLRL)                               | 21 |

|    | 2.3.3. Write Any Values, Reads Legal Values (WARL)                       | 21 |

|    | 2.4. CSR Field Modulation                                                | 21 |

|    | 2.5. Implicit Reads of CSRs                                              | 22 |

|    | 2.6. CSR Width Modulation                                                | 22 |

|    | 2.7. Explicit Accesses to CSRs Wider than XLEN                           | 22 |

| 3. | Machine-Level ISA, Version 1.13                                          | 24 |

|    | 3.1. Machine-Level CSRs                                                  | 24 |

|    | 3.1.1. Machine ISA (misa) Register                                       | 24 |

|    | 3.1.2. Machine Vendor ID (mvendorid) Register                            | 27 |

|    | 3.1.3. Machine Architecture ID (marchid) Register                        | 27 |

|    | 3.1.4. Machine Implementation ID (mimpid) Register                       | 28 |

|    | 3.1.5. Hart ID (mhartid) Register                                        | 28 |

|    | 3.1.6. Machine Status (mstatus and mstatush) Registers                   | 29 |

|    | 3.1.6.1. Privilege and Global Interrupt-Enable Stack in mstatus register | 29 |

|    | 3.1.6.2. Double Trap Control in mstatus Register                         | 30 |

|    | 3.1.6.3. Base ISA Control in mstatus Register                            | 32 |

|    | 3.1.6.4. Memory Privilege in mstatus Register                            | 32 |

|    | 3.1.6.5. Endianness Control in mstatus and mstatush Registers            | 33 |

|    | 3.1.6.6. Virtualization Support in mstatus Register                      | 34 |

|    | 3.1.6.7. Extension Context Status in mstatus Register                    | 35 |

|    | 3.1.6.8. Previous Expected Landing Pad (ELP) State in mstatus Register   | 39 |

|    | 3.1.7. Machine Trap-Vector Base-Address (mtvec) Register                 | 39 |

|    | 3.1.8. Machine Trap Delegation (medeleg and mideleg) Registers           | 40 |

|    | 3.1.9. Machine Interrupt (mip and mie) Registers                         | 41 |

|    | 3.1.10. Hardware Performance Monitor                                     | 44 |

|    | 3.1.11. Machine Counter-Enable (mcounteren) Register                     | 45 |

|    | 3.1.12. Machine Counter-Inhibit (mcountinhibit) Register                 | 46 |

|    | 3.1.13. Machine Scratch (mscratch) Register                              | 46 |

|    | 3.1.14. Machine Exception Program Counter (mepc) Register                | 47 |

|   | 3.1.15. Machine Cause (mcause) Register                                   | 47 |

|---|---------------------------------------------------------------------------|----|

|   | 3.1.16. Machine Trap Value (mtval) Register                               | 51 |

|   | 3.1.17. Machine Configuration Pointer (mconfigptr) Register               | 52 |

|   | 3.1.18. Machine Environment Configuration (menvcfg) Register              | 53 |

|   | 3.1.19. Machine Security Configuration (mseccfg) Register                 | 55 |

|   | 3.2. Machine-Level Memory-Mapped Registers                                | 56 |

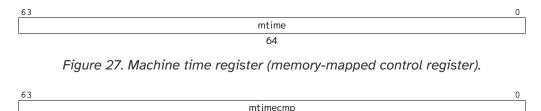

|   | 3.2.1. Machine Timer (mtime and mtimecmp) Registers                       | 56 |

|   | 3.3. Machine-Mode Privileged Instructions                                 | 57 |

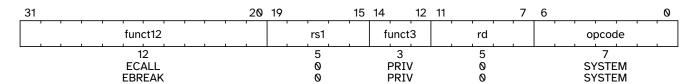

|   | 3.3.1. Environment Call and Breakpoint                                    | 57 |

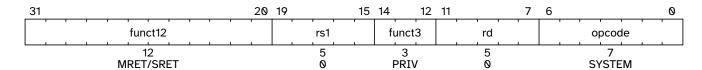

|   | 3.3.2. Trap-Return Instructions                                           | 58 |

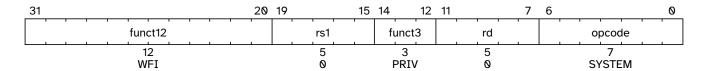

|   | 3.3.3. Wait for Interrupt                                                 | 58 |

|   | 3.3.4. Custom SYSTEM Instructions                                         | 59 |

|   | 3.4. Reset                                                                | 59 |

|   | 3.5. Non-Maskable Interrupts                                              | 60 |

|   | 3.6. Physical Memory Attributes                                           | 60 |

|   | 3.6.1. Main Memory versus I/O Regions                                     | 61 |

|   | 3.6.2. Supported Access Type PMAs                                         | 62 |

|   | 3.6.3. Atomicity PMAs                                                     | 62 |

|   | 3.6.3.1. AMO PMA                                                          | 62 |

|   | 3.6.3.2. Reservability PMA                                                | 63 |

|   | 3.6.4. Misaligned Atomicity Granule PMA                                   | 63 |

|   | 3.6.5. Memory-Ordering PMAs                                               | 64 |

|   | 3.6.6. Coherence and Cacheability PMAs                                    | 65 |

|   | 3.6.7. Idempotency PMAs                                                   |    |

|   | 3.7. Physical Memory Protection                                           | 66 |

|   | 3.7.1. Physical Memory Protection CSRs                                    |    |

|   | 3.7.1.1. Address Matching                                                 | 68 |

|   | 3.7.1.2. Locking and Privilege Mode                                       | 70 |

|   | 3.7.1.3. Priority and Matching Logic                                      | 70 |

|   | 3.7.2. Physical Memory Protection and Paging                              | 70 |

| 4 | . "Smstateen/Ssstateen" Extensions, Version 1.0                           | 72 |

|   | 4.1. State Enable Extensions                                              | 72 |

|   | 4.2. State Enable 0 Registers                                             | 74 |

|   | 4.3. Usage                                                                | 76 |

| 5 | . "Smcsrind/Sscsrind" Indirect CSR Access, Version 1.0                    | 78 |

|   | 5.1. Introduction                                                         | 78 |

|   | 5.2. Machine-level CSRs                                                   | 78 |

|   | 5.3. Supervisor-level CSRs                                                |    |

|   | 5.4. Virtual Supervisor-level CSRs                                        |    |

|   | 5.5. Access control by the state-enable CSRs                              | 82 |

|   | . "Smepmp" Extension for PMP Enhancements for memory access and execution |    |

| p | revention in Machine mode, Version 1.0                                    |    |

|   | 6.1. Introduction                                                         | 83 |

|           | 6.1.1. Threat model                                                             | 83  |

|-----------|---------------------------------------------------------------------------------|-----|

|           | 6.2. Proposal                                                                   | 84  |

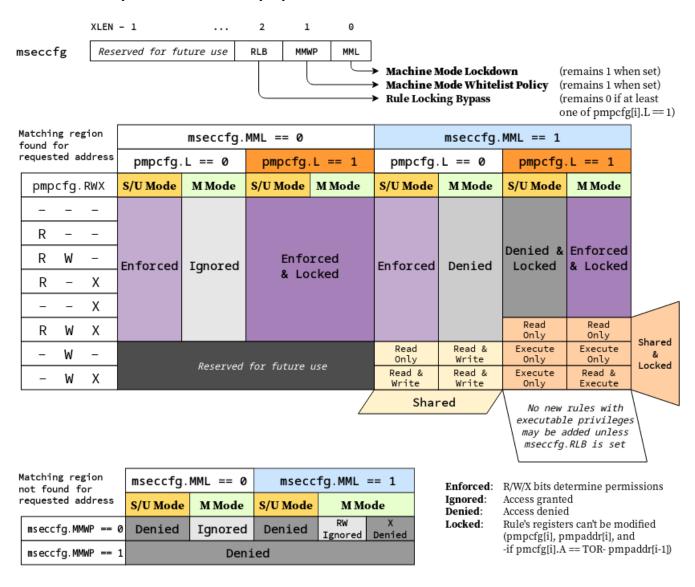

|           | 6.2.1. Truth table when mseccfg.MML is set                                      | 85  |

|           | 6.2.2. Visual representation of the proposal                                    | 86  |

|           | 6.3. Smepmp software discovery                                                  |     |

|           | 6.4. Rationale                                                                  |     |

| <b>7.</b> | . "Smcntrpmf" Cycle and Instret Privilege Mode Filtering, Version 1.0           | 90  |

|           | 7.1. Introduction                                                               | 90  |

|           | 7.2. CSRs                                                                       | 90  |

|           | 7.2.1. Machine Counter Configuration (mcyclecfg, minstretcfg) Registers         | 90  |

|           | 7.3. Counter Behavior                                                           |     |

| 8.        | . "Smrnmi" Extension for Resumable Non-Maskable Interrupts, Version 1.0         |     |

|           | 8.1. RNMI Interrupt Signals                                                     | 92  |

|           | 8.2. RNMI Handler Addresses                                                     | 92  |

|           | 8.3. RNMI CSRs                                                                  | 92  |

|           | 8.4. MNRET Instruction                                                          |     |

|           | 8.5. RNMI Operation                                                             | 94  |

| 9.        | . "Smcdeleg" Counter Delegation Extension, Version 1.0                          |     |

|           | 9.1. Counter Delegation                                                         | 95  |

|           | 9.2. Supervisor Counter Inhibit (scountinhibit) Register                        |     |

|           | 9.3. Virtualizing scountovf                                                     | 97  |

|           | 9.4. Virtualizing Local Counter Overflow Interrupts                             |     |

|           | 9. "Smdbltrp" Double Trap Extension, Version 1.0                                |     |

| 11        | I. "Smctr" Control Transfer Records Extension, Version 1.0                      |     |

|           | 11.1. CSRs                                                                      |     |

|           | 11.1.1. Machine Control Transfer Records Control Register (mctrctl)             | 99  |

|           | 11.1.2. Supervisor Control Transfer Records Control Register (sctrctl)          | 101 |

|           | 11.1.3. Virtual Supervisor Control Transfer Records Control Register (vsctrctl) | 101 |

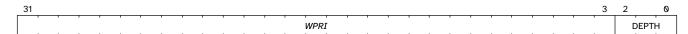

|           | 11.1.4. Supervisor Control Transfer Records Depth Register (sctrdepth)          | 102 |

|           | 11.1.5. Supervisor Control Transfer Records Status Register (sctrstatus)        | 103 |

|           | 11.2. Entry Registers                                                           | 104 |

|           | 11.2.1. Control Transfer Record Source Register (ctrsource)                     | 104 |

|           | 11.2.2. Control Transfer Record Target Register (ctrtarget)                     | 105 |

|           | 11.2.3. Control Transfer Record Metadata Register (ctrdata)                     |     |

|           | 11.3. Instructions                                                              | 106 |

|           | 11.3.1. Supervisor CTR Clear Instruction                                        |     |

|           | 11.4. State Enable Access Control                                               |     |

|           | 11.5. Behavior                                                                  | 107 |

|           | 11.5.1. Privilege Mode Transitions                                              | 107 |

|           | 11.5.1.1. Virtualization Mode Transitions                                       |     |

|           | 11.5.1.2. External Traps                                                        |     |

|           | 11.5.2. Transfer Type Filtering                                                 |     |

|           | 11.5.3. Cycle Counting                                                          | 111 |

| 11.5.4. RAS (Return Address Stack) Emulation Mode                                |                                         |

|----------------------------------------------------------------------------------|-----------------------------------------|

| 11.5.5. Freeze                                                                   | •••••                                   |

| 11.6. Custom Extensions                                                          |                                         |

| 12. Supervisor-Level ISA, Version 1.13                                           |                                         |

| 12.1. Supervisor CSRs                                                            | •••••                                   |

| 12.1.1. Supervisor Status (sstatus) Register                                     | •••••                                   |

| 12.1.1.1. Base ISA Control in sstatus Register                                   | •••••                                   |

| 12.1.1.2. Memory Privilege in sstatus Register                                   | •••••                                   |

| 12.1.1.3. Endianness Control in sstatus Register                                 |                                         |

| 12.1.1.4. Previous Expected Landing Pad (ELP) State in sstatus Register          |                                         |

| 12.1.1.5. Double Trap Control in sstatus Register                                |                                         |

| 12.1.2. Supervisor Trap Vector Base Address (stvec) Register                     |                                         |

| 12.1.3. Supervisor Interrupt (sip and sie) Registers                             | •••••                                   |

| 12.1.4. Supervisor Timers and Performance Counters                               |                                         |

| 12.1.5. Counter-Enable (scounteren) Register                                     |                                         |

| 12.1.6. Supervisor Scratch (sscratch) Register                                   | •••••                                   |

| 12.1.7. Supervisor Exception Program Counter (sepc) Register                     | •••••                                   |

| 12.1.8. Supervisor Cause (scause) Register                                       |                                         |

| 12.1.9. Supervisor Trap Value (stval) Register                                   |                                         |

| 12.1.10. Supervisor Environment Configuration (senvcfg) Register                 |                                         |

| 12.1.11. Supervisor Address Translation and Protection (satp) Register           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| 12.2. Supervisor Instructions                                                    |                                         |

| 12.2.1. Supervisor Memory-Management Fence Instruction                           |                                         |

| 12.3. Sv32: Page-Based 32-bit Virtual-Memory Systems                             |                                         |

| 12.3.1. Addressing and Memory Protection                                         |                                         |

| 12.3.2. Virtual Address Translation Process                                      |                                         |

| 12.4. Sv39: Page-Based 39-bit Virtual-Memory System                              | 1                                       |

| 12.4.1. Addressing and Memory Protection                                         | 1                                       |

| 12.5. Sv48: Page-Based 48-bit Virtual-Memory System                              |                                         |

| 12.5.1. Addressing and Memory Protection                                         | 1                                       |

| 12.6. Sv57: Page-Based 57-bit Virtual-Memory System                              | 1                                       |

| 12.6.1. Addressing and Memory Protection                                         | 1                                       |

| 13. "Svnapot" Extension for NAPOT Translation Contiguity, Version 1.0            | 1                                       |

| 14. "Svpbmt" Extension for Page-Based Memory Types, Version 1.0                  | 1                                       |

| 15. "Svinval" Extension for Fine-Grained Address-Translation Cache Invalidation, | Version                                 |

| 1.0                                                                              | 1                                       |

| 16. "Svadu" Extension for Hardware Updating of A/D Bits, Version 1.0             | 1                                       |

| 17. "Svvptc" Extension for Obviating Memory-Management Instructions after Mark   |                                         |

| Valid, Version 1.0                                                               | •                                       |

| 18. "Ssqosid" Extension for Quality-of-Service (QoS) Identifiers, Version 1.0    |                                         |

| 18.1. Supervisor Resource Management Configuration (srmcfg) register             |                                         |

| 19. "Sstc" Extension for Supervisor-mode Timer Interrupts, Version 1.0           |                                         |

| 19.1. Machine and Supervisor Level Additions                                     |                                         |

|                                                                                  |                                         |

|     | 19.1.1. Supervisor Timer (stimecmp) Register                                    | 152 |

|-----|---------------------------------------------------------------------------------|-----|

|     | 19.1.2. Machine Interrupt (mip and mie) Registers                               | 153 |

|     | 19.1.3. Supervisor Interrupt (sip and sie) Registers                            | 153 |

|     | 19.1.4. Machine Counter-Enable (mcounteren) Register                            | 153 |

| 1   | 9.2. Hypervisor Extension Additions                                             | 153 |

|     | 19.2.1. Virtual Supervisor Timer (vstimecmp) Register                           | 153 |

|     | 19.2.2. Hypervisor Interrupt (hvip, hip, and hie) Registers                     | 154 |

|     | 19.2.3. Hypervisor Counter-Enable (hcounteren) Register                         | 154 |

| 1   | 9.3. Environment Config (menvcfg and henvcfg) Support                           | 154 |

| 20. | "Sscofpmf" Extension for Count Overflow and Mode-Based Filtering, Version 1.0   | 155 |

| 2   | 20.1. Count Overflow Control                                                    | 155 |

| 2   | 20.2. Supervisor Count Overflow (scountovf) Register                            | 156 |

| 21. | "H" Extension for Hypervisor Support, Version 1.0                               | 157 |

| 2   | 21.1. Privilege Modes                                                           | 157 |

| 2   | 21.2. Hypervisor and Virtual Supervisor CSRs                                    | 158 |

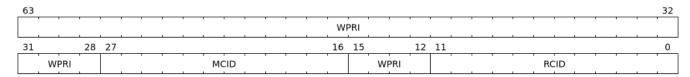

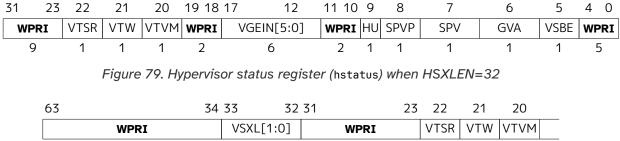

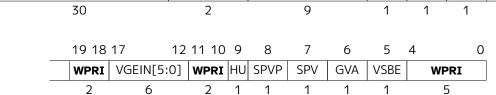

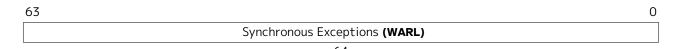

|     | 21.2.1. Hypervisor Status (hstatus) Register                                    | 159 |

|     | 21.2.2. Hypervisor Trap Delegation (hedeleg and hideleg) Registers              | 160 |

|     | 21.2.3. Hypervisor Interrupt (hvip, hip, and hie) Registers                     | 162 |

|     | 21.2.4. Hypervisor Guest External Interrupt Registers (hgeip and hgeie)         | 163 |

|     | 21.2.5. Hypervisor Environment Configuration Register (henvcfg)                 | 164 |

|     | 21.2.6. Hypervisor Counter-Enable (hcounteren) Register                         | 166 |

|     | 21.2.7. Hypervisor Time Delta (htimedelta) Register                             | 166 |

|     | 21.2.8. Hypervisor Trap Value (htval) Register                                  | 167 |

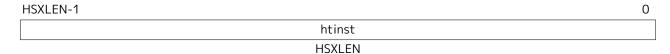

|     | 21.2.9. Hypervisor Trap Instruction (htinst) Register                           | 168 |

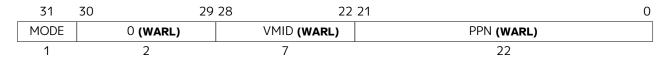

|     | 21.2.10. Hypervisor Guest Address Translation and Protection (hgatp) Register   | 168 |

|     | 21.2.11. Virtual Supervisor Status (vsstatus) Register                          | 169 |

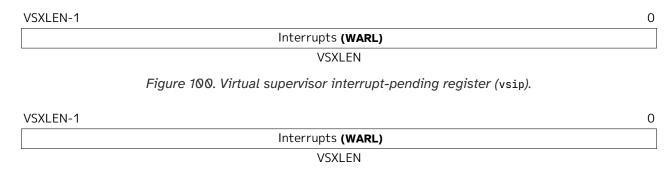

|     | 21.2.12. Virtual Supervisor Interrupt (vsip and vsie) Registers                 | 171 |

|     | 21.2.13. Virtual Supervisor Trap Vector Base Address (vstvec) Register          | 172 |

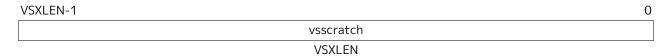

|     | 21.2.14. Virtual Supervisor Scratch (vsscratch) Register                        | 172 |

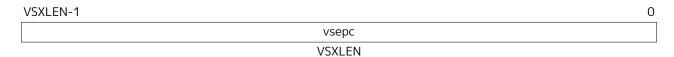

|     | 21.2.15. Virtual Supervisor Exception Program Counter (vsepc) Register          | 172 |

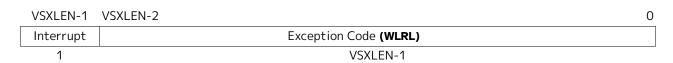

|     | 21.2.16. Virtual Supervisor Cause (vscause) Register                            | 172 |

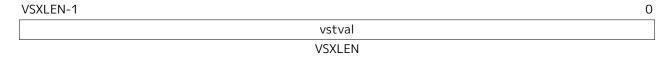

|     | 21.2.17. Virtual Supervisor Trap Value (vstval) Register                        | 173 |

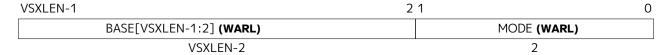

|     | 21.2.18. Virtual Supervisor Address Translation and Protection (vsatp) Register | 173 |

| 2   | 21.3. Hypervisor Instructions                                                   | 174 |

|     | 21.3.1. Hypervisor Virtual-Machine Load and Store Instructions                  | 174 |

|     | 21.3.2. Hypervisor Memory-Management Fence Instructions                         | 175 |

| 2   | 21.4. Machine-Level CSRs                                                        | 176 |

|     | 21.4.1. Machine Status (mstatus and mstatush) Registers                         | 176 |

|     | 21.4.2. Machine Interrupt Delegation (mideleg) Register                         | 178 |

|     | 21.4.3. Machine Interrupt (mip and mie) Registers                               | 178 |

|     | 21.4.4. Machine Second Trap Value (mtval2) Register                             | 179 |

|     | 21.4.5. Machine Trap Instruction (mtinst) Register                              | 179 |

| 2   | 21.5. Two-Stage Address Translation                                             | 180 |

| 21.5.1. Guest Physical Address Translation                                | 180 |

|---------------------------------------------------------------------------|-----|

| 21.5.2. Guest-Page Faults                                                 | 182 |

| 21.5.3. Memory-Management Fences                                          | 182 |

| 21.6. Traps                                                               | 183 |

| 21.6.1. Trap Cause Codes                                                  | 183 |

| 21.6.2. Trap Entry                                                        | 187 |

| 21.6.3. Transformed Instruction or Pseudoinstruction for mtinst or htinst | 188 |

| 21.6.4. Trap Return                                                       | 192 |

| 22. Control-flow Integrity (CFI)                                          | 194 |

| 22.1. Landing Pad (Zicfilp)                                               | 194 |

| 22.1.1. Landing-Pad-Enabled (LPE) State                                   | 194 |

| 22.1.2. Preserving Expected Landing Pad State on Traps                    | 195 |

| 22.2. Shadow Stack (Zicfiss)                                              | 196 |

| 22.2.1. Shadow Stack Pointer (ssp) CSR access control                     | 196 |

| 22.2.2. Shadow-Stack-Enabled (SSE) State                                  | 196 |

| 22.2.3. Shadow Stack Memory Protection                                    | 197 |

| 23. "Ssdbltrp" Double Trap Extension, Version 1.0                         | 200 |

| 24. Pointer Masking Extensions, Version 1.0.0                             | 201 |

| 24.1. Introduction                                                        | 201 |

| 24.2. Background                                                          | 201 |

| 24.2.1. Definitions                                                       | 201 |

| 24.2.2. The "Ignore" Transformation                                       | 202 |

| 24.2.3. Example                                                           | 203 |

| 24.2.4. Determining the Value of PMLEN                                    | 203 |

| 24.2.5. Pointer Masking and Privilege Modes                               | 204 |

| 24.2.6. Memory Accesses Subject to Pointer Masking                        | 205 |

| 24.2.7. Pointer Masking Extensions                                        | 206 |

| 24.3. ISA Extensions                                                      | 207 |

| 24.3.1. Ssnpm                                                             | 207 |

| 24.3.2. Smnpm                                                             | 208 |

| 24.3.3. Smmpm                                                             | 208 |

| 24.3.4. Interaction with SFENCE.VMA                                       | 208 |

| 24.3.5. Interaction with Two-Stage Address Translation                    | 208 |

| 24.3.6. Number of Masked Bits                                             | 209 |

| 25. RISC-V Privileged Instruction Set Listings                            | 210 |

| 26. History                                                               | 212 |

| 26.1. Research Funding at UC Berkeley                                     | 212 |

| Bibliography                                                              | 213 |

## **Preamble**

Contributors to all versions of the spec in alphabetical order (please contact editors to suggest corrections): Krste Asanović, Peter Ashenden, Rimas Avižienis, Jacob Bachmeyer, Allen J. Baum, Jonathan Behrens, Paolo Bonzini, Ruslan Bukin, Christopher Celio, Chuanhua Chang, David Chisnall, Anthony Coulter, Palmer Dabbelt, Monte Dalrymple, Paul Donahue, Greg Favor, Dennis Ferguson, Marc Gauthier, Andy Glew, Gary Guo, Mike Frysinger, John Hauser, David Horner, Olof Johansson, David Kruckemyer, Yunsup Lee, Daniel Lustig, Andrew Lutomirski, Martin Maas, Prashanth Mundkur, Jonathan Neuschäfer, Rishiyur Nikhil, Stefan O'Rear, Albert Ou, John Ousterhout, David Patterson, Dmitri Pavlov, Kade Phillips, Josh Scheid, Colin Schmidt, Michael Taylor, Wesley Terpstra, Matt Thomas, Tommy Thorn, Ray VanDeWalker, Megan Wachs, Steve Wallach, Andrew Waterman, Claire Wolf, Adam Zabrocki, and Reinoud Zandijk...

This document is released under a Creative Commons Attribution 4.0 International License.

This document is a derivative of the RISC-V privileged specification version 1.9.1 released under following license: ©2010-2017 Andrew Waterman, Yunsup Lee, Rimas Avižienis, David Patterson, Krste Asanović. Creative Commons Attribution 4.0 International License.

## **Preface**

## Preface to Version 20241101

This document describes the RISC-V privileged architecture. This release, version 20241101, contains the following versions of the RISC-V ISA modules:

| Module                             | Version | Status   |

|------------------------------------|---------|----------|

| Machine ISA                        | 1.14    | Draft    |

| Smstateen Extension                | 1.0     | Ratified |

| <b>Smcsrind/Sscsrind Extension</b> | 1.0     | Ratified |

| Smepmp Extension                   | 1.0     | Ratified |

| <b>Smcntrpmf Extension</b>         | 1.0     | Ratified |

| Smrnmi Extension                   | 1.0     | Ratified |

| Smcdeleg Extension                 | 1.0     | Ratified |

| Smdbltrp Extension                 | 1.0     | Ratified |

| Supervisor ISA                     | 1.14    | Draft    |

| Svade Extension                    | 1.0     | Ratified |

| <b>Synapot Extension</b>           | 1.0     | Ratified |

| Sypbmt Extension                   | 1.0     | Ratified |

| <b>Svinval Extension</b>           | 1.0     | Ratified |

| Svadu Extension                    | 1.0     | Ratified |

| Sstc Extension                     | 1.0     | Ratified |

| Sscofpmf Extension                 | 1.0     | Ratified |

| Ssdbltrp Extension                 | 1.0     | Ratified |

| Ssqosid Extension                  | 1.0     | Ratified |

| Hypervisor ISA                     | 1.0     | Ratified |

| <b>Shlcofideleg Extension</b>      | 1.0     | Ratified |

| <b>Svvptc Extension</b>            | 1.0     | Ratified |

The following changes have been made since version 1.13 of the Machine and Supervisor ISAs, which, while not strictly backwards compatible, are not anticipated to cause software portability problems in practice:

• (None yet)

Additionally, the following compatible changes have been made to the Machine and Supervisor ISAs since version 1.13:

• Defined the mstateen0 P1P14 field.

Finally, the following clarifications and document improvements have been made since the last document release:

• (None yet)

## Preface to Version 20241017

This document describes the RISC-V privileged architecture. This release, version 20241017, contains the following versions of the RISC-V ISA modules:

| Module                             | Version | Status   |

|------------------------------------|---------|----------|

| Machine ISA                        | 1.13    | Ratified |

| Smstateen Extension                | 1.0     | Ratified |

| <b>Smcsrind/Sscsrind Extension</b> | 1.0     | Ratified |

| Smepmp                             | 1.0     | Ratified |

| Smcntrpmf                          | 1.0     | Ratified |

| Smrnmi Extension                   | 1.0     | Ratified |

| Smcdeleg                           | 1.0     | Ratified |

| Smdbltrp                           | 1.0     | Ratified |

| Supervisor ISA                     | 1.13    | Ratified |

| <b>Svade Extension</b>             | 1.0     | Ratified |

| <b>Synapot Extension</b>           | 1.0     | Ratified |

| Sypbmt Extension                   | 1.0     | Ratified |

| <b>Svinval Extension</b>           | 1.0     | Ratified |

| Svadu Extension                    | 1.0     | Ratified |

| Sstc                               | 1.0     | Ratified |

| Sscofpmf                           | 1.0     | Ratified |

| Ssdbltrp                           | 1.0     | Ratified |

| Hypervisor ISA                     | 1.0     | Ratified |

| Shlcofideleg                       | 1.0     | Ratified |

| Svvptc                             | 1.0     | Ratified |

The following changes have been made since version 1.12 of the Machine and Supervisor ISAs, which, while not strictly backwards compatible, are not anticipated to cause software portability problems in practice:

- Redefined misa.MXL to be read-only, making MXLEN a constant.

- Added the constraint that SXLEN≥UXLEN.

Additionally, the following compatible changes have been made to the Machine and Supervisor ISAs since version 1.12:

- Defined the misa.B field to reflect that the B extension has been implemented.

- Defined the misa.V field to reflect that the V extension has been implemented.

- Defined the RV32-only medelegh and hedelegh CSRs.

- Defined the misaligned atomicity granule PMA, superseding the proposed Zam extension.

- Allocated interrupt 13 for Sscofpmf LCOFI interrupt.

- Defined hardware error and software check exception codes.

- Specified synchronization requirements when changing the PBMTE fields in menvcfg and henvcfg.

- Exposed count-overflow interrupts to VS-mode via the Shlcofideleg extension.

- Relaxed behavior of some HINTs when MXLEN > XLEN.

Finally, the following clarifications and document improvements have been made since the last document release:

- Transliterated the document from LaTeX into AsciiDoc.

- Included all ratified extensions through March 2024.

- Clarified that "platform- or custom-use" interrupts are actually "platform-use interrupts", where the platform can choose to make some custom.

- Clarified semantics of explicit accesses to CSRs wider than XLEN bits.

- Clarified that MXLEN≥SXLEN.

- Clarified that WFI is not a HINT instruction.

- Clarified that VS-stage page-table accesses set G-stage A/D bits.

- Clarified ordering rules when PBMT=IO is used on main-memory regions.

- Clarified ordering rules for hardware A/D bit updates.

- Clarified that, for a given exception cause, xtval might sometimes be set to a nonzero value but sometimes not.

- Clarified exception behavior of unimplemented or inaccessible CSRs.

- Clarified that Sypbmt allows implementations to override additional PMAs.

- Replaced the concept of vacant memory regions with inaccessible memory or I/O regions.

- Clarified that timer and count-overflow interrupts' arrival in interrupt-pending registers is not immediate.

- Clarified that MXR affects only explicit memory accesses.

### Preface to Version 20211203

This document describes the RISC-V privileged architecture. This release, version 20211203, contains the following versions of the RISC-V ISA modules:

| Module                   | Version | Status   |

|--------------------------|---------|----------|

| Machine ISA              | 1.12    | Ratified |

| Supervisor ISA           | 1.12    | Ratified |

| <b>Svnapot Extension</b> | 1.0     | Ratified |

| <b>Sypbmt Extension</b>  | 1.0     | Ratified |

| <b>Svinval Extension</b> | 1.0     | Ratified |

| Hypervisor ISA           | 1.0     | Ratified |

The following changes have been made since version 1.11, which, while not strictly backwards compatible, are not anticipated to cause software portability problems in practice:

- Changed MRET and SRET to clear mstatus.MPRV when leaving M-mode.

- Reserved additional satp patterns for future use.

- Stated that the scause Exception Code field must implement bits 4–0 at minimum.

- Relaxed I/O regions have been specified to follow RVWMO. The previous specification implied that PPO rules other than fences and acquire/release annotations did not apply.

- Constrained the LR/SC reservation set size and shape when using page-based virtual memory.

- PMP changes require an SFENCE.VMA on any hart that implements page-based virtual memory, even if VM is not currently enabled.

- Allowed for speculative updates of page table entry A bits.

- Clarify that if the address-translation algorithm non-speculatively reaches a PTE in which a bit reserved for future standard use is set, a page-fault exception must be raised.

Additionally, the following compatible changes have been made since version 1.11:

- Removed the N extension.

- Defined the mandatory RV32-only CSR mstatush, which contains most of the same fields as the upper 32 bits of RV64's mstatus.

- Defined the mandatory CSR mconfigptr, which if nonzero contains the address of a configuration data structure.

- Defined optional mseccfg and mseccfgh CSRs, which control the machine's security configuration.

- Defined menvcfg, henvcfg, and senvcfg CSRs (and RV32-only menvcfgh and henvcfgh CSRs), which

control various characteristics of the execution environment.

- Designated part of SYSTEM major opcode for custom use.

- Permitted the unconditional delegation of less-privileged interrupts.

- Added optional big-endian and bi-endian support.

- Made priority of load/store/AMO address-misaligned exceptions implementation-defined relative to load/store/AMO page-fault and access-fault exceptions.

- PMP reset values are now platform-defined.

- An additional 48 optional PMP registers have been defined.

- Slightly relaxed the atomicity requirement for A and D bit updates performed by the implementation.

- Clarify the architectural behavior of address-translation caches

- Added Sv57 and Sv57x4 address translation modes.

- Software breakpoint exceptions are permitted to write either 0 or the pc to xtval.

- Clarified that bare S-mode need not support the SFENCE.VMA instruction.

- Specified relaxed constraints for implicit reads of non-idempotent regions.

- Added the Svnapot Standard Extension, along with the N bit in Sv39, Sv48, and Sv57 PTEs.

- Added the Svpbmt Standard Extension, along with the PBMT bits in Sv39, Sv48, and Sv57 PTEs.

- Added the Svinval Standard Extension and associated instructions.

Finally, the hypervisor architecture proposal has been extensively revised.

## Preface to Version 1.11

This is version 1.11 of the RISC-V privileged architecture. The document contains the following versions of the RISC-V ISA modules:

| Module                                          | Version              | Status                        |

|-------------------------------------------------|----------------------|-------------------------------|

| Machine ISA<br>Supervisor ISA<br>Hypervisor ISA | <b>1.11 1.11</b> 0.3 | Ratified<br>Ratified<br>Draft |

Changes from version 1.10 include:

- Moved Machine and Supervisor spec to **Ratified** status.

- Improvements to the description and commentary.

- Added a draft proposal for a hypervisor extension.

- Specified which interrupt sources are reserved for standard use.

- Allocated some synchronous exception causes for custom use.

- Specified the priority ordering of synchronous exceptions.

- Added specification that xRET instructions may, but are not required to, clear LR reservations if A

extension present.

- The virtual-memory system no longer permits supervisor mode to execute instructions from user pages, regardless of the SUM setting.

- Clarified that ASIDs are private to a hart, and added commentary about the possibility of a future global-ASID extension.

- SFENCE.VMA semantics have been clarified.

- Made the mstatus.MPP field WARL, rather than WLRL.

- Made the unused xip fields WPRI, rather than WIRI.

- Made the unused misa fields WARL, rather than WIRI.

- Made the unused pmpaddr and pmpcfg fields **WARL**, rather than **WIRI**.

- Required all harts in a system to employ the same PTE-update scheme as each other.

- Rectified an editing error that misdescribed the mechanism by which mstatus.xIE is written upon an exception.

- Described scheme for emulating misaligned AMOs.

- Specified the behavior of the misa and xepc registers in systems with variable IALIGN.

- Specified the behavior of writing self-contradictory values to the misa register.

- Defined the mcountinhibit CSR, which stops performance counters from incrementing to reduce energy consumption.

- Specified semantics for PMP regions coarser than four bytes.

- Specified contents of CSRs across XLEN modification.

- Moved PLIC chapter into its own document.

## Preface to Version 1.10

This is version 1.10 of the RISC-V privileged architecture proposal. Changes from version 1.9.1 include:

- The previous version of this document was released under a Creative Commons Attribution 4.0

International License by the original authors, and this and future versions of this document will be released under the same license.

- The explicit convention on shadow CSR addresses has been removed to reclaim CSR space. Shadow CSRs can still be added as needed.

- The mvendorid register now contains the JEDEC code of the core provider as opposed to a code supplied by the Foundation. This avoids redundancy and offloads work from the Foundation.

- The interrupt-enable stack discipline has been simplified.

- An optional mechanism to change the base ISA used by supervisor and user modes has been added to the mstatus CSR, and the field previously called Base in misa has been renamed to MXL for consistency.

- Clarified expected use of XS to summarize additional extension state status fields in mstatus.

- Optional vectored interrupt support has been added to the mtvec and stvec CSRs.

- The SEIP and UEIP bits in the mip CSR have been redefined to support software injection of external interrupts.

- The mbadaddr register has been subsumed by a more general mtval register that can now capture bad instruction bits on an illegal instruction fault to speed instruction emulation.

- The machine-mode base-and-bounds translation and protection schemes have been removed from the specification as part of moving the virtual memory configuration to sptbr (now satp). Some of the motivation for the base and bound schemes are now covered by the PMP registers, but space remains available in mstatus to add these back at a later date if deemed useful.

- In systems with only M-mode, or with both M-mode and U-mode but without U-mode trap support, the medeleg and mideleg registers now do not exist, whereas previously they returned zero.

- Virtual-memory page faults now have mcause values distinct from physical-memory access faults.

Page-fault exceptions can now be delegated to S-mode without delegating exceptions generated by PMA and PMP checks.

- An optional physical-memory protection (PMP) scheme has been proposed.

- The supervisor virtual memory configuration has been moved from the mstatus register to the sptbr register. Accordingly, the sptbr register has been renamed to satp (Supervisor Address Translation and Protection) to reflect its broadened role.

- The SFENCE.VM instruction has been removed in favor of the improved SFENCE.VMA instruction.

- The mstatus bit MXR has been exposed to S-mode via sstatus.

- The polarity of the PUM bit in sstatus has been inverted to shorten code sequences involving MXR.

The bit has been renamed to SUM.

- Hardware management of page-table entry Accessed and Dirty bits has been made optional;

simpler implementations may trap to software to set them.

- The counter-enable scheme has changed, so that S-mode can control availability of counters to U-mode.

- H-mode has been removed, as we are focusing on recursive virtualization support in S-mode. The

encoding space has been reserved and may be repurposed at a later date.

- A mechanism to improve virtualization performance by trapping S-mode virtual-memory management operations has been added.

- The Supervisor Binary Interface (SBI) chapter has been removed, so that it can be maintained as a separate specification.

#### Preface to Version 1.9.1

This is version 1.9.1 of the RISC-V privileged architecture proposal. Changes from version 1.9 include:

- Numerous additions and improvements to the commentary sections.

- Change configuration string proposal to be use a search process that supports various formats including Device Tree String and flattened Device Tree.

- Made misa optionally writable to support modifying base and supported ISA extensions. CSR address of misa changed.

- Added description of debug mode and debug CSRs.

- Added a hardware performance monitoring scheme. Simplified the handling of existing hardware counters, removing privileged versions of the counters and the corresponding delta registers.

- Fixed description of SPIE in presence of user-level interrupts.

## **Chapter 1. Introduction**

This document describes the RISC-V privileged architecture, which covers all aspects of RISC-V systems beyond the unprivileged ISA, including privileged instructions as well as additional functionality required for running operating systems and attaching external devices.

Commentary on our design decisions is formatted as in this paragraph, and can be skipped if the reader is only interested in the specification itself.

We briefly note that the entire privileged-level design described in this document could be replaced with an entirely different privileged-level design without changing the unprivileged ISA, and possibly without even changing the ABI. In particular, this privileged specification was designed to run existing popular operating systems, and so embodies the conventional level-based protection model. Alternate privileged specifications could embody other more flexible protection-domain models. For simplicity of expression, the text is written as if this was the only possible privileged architecture.

## 1.1. RISC-V Privileged Software Stack Terminology

This section describes the terminology we use to describe components of the wide range of possible privileged software stacks for RISC-V.

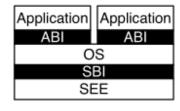

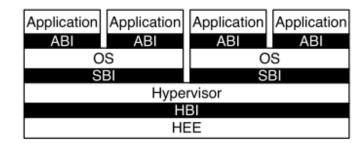

Figure 1 shows some of the possible software stacks that can be supported by the RISC-V architecture. The left-hand side shows a simple system that supports only a single application running on an application execution environment (AEE). The application is coded to run with a particular application binary interface (ABI). The ABI includes the supported user-level ISA plus a set of ABI calls to interact with the AEE. The ABI hides details of the AEE from the application to allow greater flexibility in implementing the AEE. The same ABI could be implemented natively on multiple different host OSs, or could be supported by a user-mode emulation environment running on a machine with a different native ISA.

Our graphical convention represents abstract interfaces using black boxes with white text, to separate them from concrete instances of components implementing the interfaces.

Figure 1. Different implementation stacks supporting various forms of privileged execution.

The middle configuration shows a conventional operating system (OS) that can support multiprogrammed execution of multiple applications. Each application communicates over an ABI with the OS, which provides the AEE. Just as applications interface with an AEE via an ABI, RISC-V operating systems interface with a supervisor execution environment (SEE) via a supervisor binary

interface (SBI). An SBI comprises the user-level and supervisor-level ISA together with a set of SBI function calls. Using a single SBI across all SEE implementations allows a single OS binary image to run on any SEE. The SEE can be a simple boot loader and BIOS-style IO system in a low-end hardware platform, or a hypervisor-provided virtual machine in a high-end server, or a thin translation layer over a host operating system in an architecture simulation environment.

Most supervisor-level ISA definitions do not separate the SBI from the execution environment and/or the hardware platform, complicating virtualization and bring-up of new hardware platforms.

The rightmost configuration shows a virtual machine monitor configuration where multiple multiprogrammed OSs are supported by a single hypervisor. Each OS communicates via an SBI with the hypervisor, which provides the SEE. The hypervisor communicates with the hypervisor execution environment (HEE) using a hypervisor binary interface (HBI), to isolate the hypervisor from details of the hardware platform.

The ABI, SBI, and HBI are still a work-in-progress, but we are now prioritizing support for Type-2 hypervisors where the SBI is provided recursively by an S-mode OS.

Hardware implementations of the RISC-V ISA will generally require additional features beyond the privileged ISA to support the various execution environments (AEE, SEE, or HEE).

## 1.2. Privilege Levels

At any time, a RISC-V hardware thread (*hart*) is running at some privilege level encoded as a mode in one or more CSRs (control and status registers). Three RISC-V privilege levels are currently defined as shown in Table 1.

| Level | Encoding | Name             | Abbreviation |

|-------|----------|------------------|--------------|

| 0     | 00       | User/Application | U            |

| 1     | 01       | Supervisor       | S            |

| 2     | 10       | Reserved         |              |

| 3     | 11       | Machine          | M            |

Table 1. RISC-V privilege levels.

Privilege levels are used to provide protection between different components of the software stack, and attempts to perform operations not permitted by the current privilege mode will cause an exception to be raised. These exceptions will normally cause traps into an underlying execution environment.

In the description, we try to separate the privilege level for which code is written, from the privilege mode in which it runs, although the two are often tied. For example, a supervisor-level operating system can run in supervisor-mode on a system with three privilege modes, but can also run in user-mode under a classic virtual machine monitor on systems with two or more privilege modes. In both cases, the same supervisor-level operating system binary code can be used, coded to a supervisor-level SBI and hence expecting to be able to use supervisor-level privileged instructions and CSRs. When running a guest OS in user mode, all supervisor-level actions will be trapped and emulated by the SEE running in the higher-privilege level.

The machine level has the highest privileges and is the only mandatory privilege level for a RISC-V hardware platform. Code run in machine-mode (M-mode) is usually inherently trusted, as it has low-level access to the machine implementation. M-mode can be used to manage secure execution environments on RISC-V. User-mode (U-mode) and supervisor-mode (S-mode) are intended for conventional application and operating system usage respectively.

Each privilege level has a core set of privileged ISA extensions with optional extensions and variants. For example, machine-mode supports an optional standard extension for memory protection. Also, supervisor mode can be extended to support Type-2 hypervisor execution as described in Chapter 21.

Implementations might provide anywhere from 1 to 3 privilege modes trading off reduced isolation for lower implementation cost, as shown in Table 2.

|                  | • •                    |                                             |

|------------------|------------------------|---------------------------------------------|

| Number of levels | <b>Supported Modes</b> | Intended Usage                              |

| 1                | М                      | Simple embedded systems                     |

| 2                | M, U                   | Secure embedded systems                     |

| 3                | M, S, U                | Systems running Unix-like operating systems |

Table 2. Supported combination of privilege modes.

All hardware implementations must provide M-mode, as this is the only mode that has unfettered access to the whole machine. The simplest RISC-V implementations may provide only M-mode, though this will provide no protection against incorrect or malicious application code.

The lock feature of the optional PMP facility can provide some limited protection even with only M-mode implemented.

Many RISC-V implementations will also support at least user mode (U-mode) to protect the rest of the system from application code. Supervisor mode (S-mode) can be added to provide isolation between a supervisor-level operating system and the SEE.

A hart normally runs application code in U-mode until some trap (e.g., a supervisor call or a timer interrupt) forces a switch to a trap handler, which usually runs in a more privileged mode. The hart will then execute the trap handler, which will eventually resume execution at or after the original trapped instruction in U-mode. Traps that increase privilege level are termed *vertical* traps, while traps that remain at the same privilege level are termed *horizontal* traps. The RISC-V privileged architecture provides flexible routing of traps to different privilege layers.

Horizontal traps can be implemented as vertical traps that return control to a horizontal trap handler in the less-privileged mode.

## 1.3. Debug Mode

Implementations may also include a debug mode to support off-chip debugging and/or manufacturing test. Debug mode (D-mode) can be considered an additional privilege mode, with even more access than M-mode. The separate debug specification proposal describes operation of a RISC-V hart in debug mode. Debug mode reserves a few CSR addresses that are only accessible in D-mode, and may also reserve some portions of the physical address space on a platform.

# **Chapter 2. Control and Status Registers (CSRs)**

The SYSTEM major opcode is used to encode all privileged instructions in the RISC-V ISA. These can be divided into two main classes: those that atomically read-modify-write control and status registers (CSRs), which are defined in the Zicsr extension, and all other privileged instructions. The privileged architecture requires the Zicsr extension; which other privileged instructions are required depends on the privileged-architecture feature set.

In addition to the unprivileged state described in Volume I of this manual, an implementation may contain additional CSRs, accessible by some subset of the privilege levels using the CSR instructions described in Volume I. In this chapter, we map out the CSR address space. The following chapters describe the function of each of the CSRs according to privilege level, as well as the other privileged instructions which are generally closely associated with a particular privilege level. Note that although CSRs and instructions are associated with one privilege level, they are also accessible at all higher privilege levels.

Standard CSRs do not have side effects on reads but may have side effects on writes.

## 2.1. CSR Address Mapping Conventions

The standard RISC-V ISA sets aside a 12-bit encoding space (csr[11:0]) for up to 4,096 CSRs. By convention, the upper 4 bits of the CSR address (csr[11:8]) are used to encode the read and write accessibility of the CSRs according to privilege level as shown in Table 3. The top two bits (csr[11:10]) indicate whether the register is read/write (00,01, or 10) or read-only (11). The next two bits (csr[9:8]) encode the lowest privilege level that can access the CSR.

The CSR address convention uses the upper bits of the CSR address to encode default access privileges. This simplifies error checking in the hardware and provides a larger CSR space, but does constrain the mapping of CSRs into the address space.

Implementations might allow a more-privileged level to trap otherwise permitted CSR accesses by a less-privileged level to allow these accesses to be intercepted. This change should be transparent to the less-privileged software.

Instructions that access a non-existent CSR are reserved. Attempts to access a CSR without appropriate privilege level raise illegal-instruction exceptions or, as described in Section 21.6.1, virtual-instruction exceptions. Attempts to write a read-only register raise illegal-instruction exceptions. A read/write register might also contain some bits that are read-only, in which case writes to the read-only bits are ignored.

Table 3 also indicates the convention to allocate CSR addresses between standard and custom uses. The CSR addresses designated for custom uses will not be redefined by future standard extensions.

Machine-mode standard read-write CSRs 0x7A0-0x7BF are reserved for use by the debug system. Of these CSRs, 0x7A0-0x7AF are accessible to machine mode, whereas 0x7B0-0x7BF are only visible to debug mode. Implementations should raise illegal-instruction exceptions on machine-mode access to the latter set of registers.

Effective virtualization requires that as many instructions run natively as possible inside a virtualized environment, while any privileged accesses trap to the virtual machine monitor. (Goldberg, 1974) CSRs that are read-only at some lower privilege level are shadowed into separate CSR addresses if they are made read-write at a

higher privilege level. This avoids trapping permitted lower-privilege accesses while still causing traps on illegal accesses. Currently, the counters are the only shadowed CSRs.

# 2.2. CSR Listing

Table 4-Table 8 list the CSRs that have currently been allocated CSR addresses. The timers, counters, and floating-point CSRs are standard unprivileged CSRs. The other registers are used by privileged code, as described in the following chapters. Note that not all registers are required on all implementations.

Table 3. Allocation of RISC-V CSR address ranges.

| CSR Address           |                                  |       | Hex           | Use and Accessibility |  |  |  |  |  |  |  |

|-----------------------|----------------------------------|-------|---------------|-----------------------|--|--|--|--|--|--|--|

| [11:10]               | [9:8]                            | [7:4] |               |                       |  |  |  |  |  |  |  |

|                       | Unprivileged and User-Level CSRs |       |               |                       |  |  |  |  |  |  |  |

| 00                    | 00                               | XXXX  | 0x000-0x0FF   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 00                               | XXXX  | 0x400-0x4FF   | Standard read/write   |  |  |  |  |  |  |  |

| 10                    | 00                               | XXXX  | 0x800-0x8FF   | Custom read/write     |  |  |  |  |  |  |  |

| 11                    | 00                               | OXXX  | 0xC00-0xC7F   | Standard read-only    |  |  |  |  |  |  |  |

| 11                    | 00                               | 10XX  | 0xC80-0xCBF   | Standard read-only    |  |  |  |  |  |  |  |

| 11                    | 00                               | 11XX  | 0xCCO-0xCFF   | Custom read-only      |  |  |  |  |  |  |  |

| Supervisor-Level CSRs |                                  |       |               |                       |  |  |  |  |  |  |  |

| 00                    | 01                               | xxxx  | 0x100-0x1FF   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 01                               | 0XXX  | 0x500-0x57F   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 01                               | 10XX  | 0x580-0x5BF   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 01                               | 11XX  | 0x5C0-0x5FF   | Custom read/write     |  |  |  |  |  |  |  |

| 10                    | 01                               | 0XXX  | 0x900-0x97F   | Standard read/write   |  |  |  |  |  |  |  |

| 10                    | 01                               | 10XX  | 0x980-0x9BF   | Standard read/write   |  |  |  |  |  |  |  |

| 10                    | 01                               | 11XX  | 0x9C0-0x9FF   | Custom read/write     |  |  |  |  |  |  |  |

| 11                    | 01                               | 0XXX  | 0xD00-0xD7F   | Standard read-only    |  |  |  |  |  |  |  |

| 11                    | 01                               | 10XX  | 0xD80-0xDBF   | Standard read-only    |  |  |  |  |  |  |  |

| 11                    | 01                               | 11XX  | 0xDC0-0xDFF   | Custom read-only      |  |  |  |  |  |  |  |

|                       |                                  |       | Hypervisor ar | nd VS CSRs            |  |  |  |  |  |  |  |

| 00                    | 10                               | XXXX  | 0x200-0x2FF   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 10                               | 0XXX  | 0x600-0x67F   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 10                               | 10XX  | 0x680-0x6BF   | Standard read/write   |  |  |  |  |  |  |  |

| 01                    | 10                               | 11XX  | 0x6C0-0x6FF   | Custom read/write     |  |  |  |  |  |  |  |

| 10                    | 10                               | 0XXX  | 0xA00-0xA7F   | Standard read/write   |  |  |  |  |  |  |  |

| 10                    | 10                               | 10XX  | 0xA80-0xABF   | Standard read/write   |  |  |  |  |  |  |  |

| 10 | 10 | 11XX | 0xAC0-0xAFF | Custom read/write              |  |  |  |  |  |

|----|----|------|-------------|--------------------------------|--|--|--|--|--|

| 11 | 10 | 0XXX | 0xE00-0xE7F | Standard read-only             |  |  |  |  |  |

| 11 | 10 | 10XX | 0xE80-0xEBF | Standard read-only             |  |  |  |  |  |

| 11 | 10 | 11XX | 0xECO-0xEFF | Custom read-only               |  |  |  |  |  |

|    |    |      | Machine-Le  | evel CSRs                      |  |  |  |  |  |

| 00 | 11 | XXXX | 0x300-0x3FF | Standard read/write            |  |  |  |  |  |

| 01 | 11 | 0XXX | 0x700-0x77F | Standard read/write            |  |  |  |  |  |

| 01 | 11 | 100X | 0x780-0x79F | Standard read/write            |  |  |  |  |  |

| 01 | 11 | 1010 | 0x7A0-0x7AF | Standard read/write debug CSRs |  |  |  |  |  |

| 01 | 11 | 1011 | 0x7B0-0x7BF | Debug-mode-only CSRs           |  |  |  |  |  |

| 01 | 11 | 11XX | 0x7C0-0x7FF | Custom read/write              |  |  |  |  |  |

| 10 | 11 | 0XXX | 0xB00-0xB7F | Standard read/write            |  |  |  |  |  |

| 10 | 11 | 10XX | 0xB80-0xBBF | Standard read/write            |  |  |  |  |  |

| 10 | 11 | 11XX | 0xBC0-0xBFF | Custom read/write              |  |  |  |  |  |

| 11 | 11 | 0XXX | 0xF00-0xF7F | Standard read-only             |  |  |  |  |  |

| 11 | 11 | 10XX | 0xF80-0xFBF | Standard read-only             |  |  |  |  |  |

| 11 | 11 | 11XX | 0xFC0-0xFFF | Custom read-only               |  |  |  |  |  |

Table 4. Currently allocated RISC-V unprivileged CSR addresses.

| Number | Privilege | Name             | Description                                               |

|--------|-----------|------------------|-----------------------------------------------------------|

|        |           | U                | Inprivileged Floating-Point CSRs                          |

| 0x001  | URW       | fflags           | Floating-Point Accrued Exceptions.                        |

| 0x002  | URW       | frm              | Floating-Point Dynamic Rounding Mode.                     |

| 0x003  | URW       | fcsr             | Floating-Point Control and Status Register (frm +fflags). |

|        |           |                  | Unprivileged Vector CSRs                                  |

| 0x008  | URW       | vstart           | Vector start position.                                    |

| 0x009  | URW       | vxsat            | Fixed-point accrued saturation flag.                      |

| 0x00A  | URW       | vxrm             | Fixed-point rounding mode.                                |

| 0x00F  | URW       | vcsr             | Vector control and status register.                       |

| 0xC20  | URO       | vl               | Vector length.                                            |

| 0xC21  | URO       | vtype            | Vector data type register.                                |

| 0xC22  | URO       | vlenb            | Vector register length in bytes.                          |

|        |           | Ur               | nprivileged Zicfiss extension CSR                         |

| 0x011  | URW       | ssp              | Shadow Stack Pointer.                                     |

|        |           | Unpriv           | ileged Entropy Source Extension CSR                       |

| 0x015  | URW       | seed             | Seed for cryptographic random bit generators.             |

|        |           |                  | Unprivileged Counter/Timers                               |

| 0×C00  | URO       | cycle            | Cycle counter for RDCYCLE instruction.                    |

| 0xC01  | URO       | time             | Timer for RDTIME instruction.                             |

| 0xC02  | URO       | instret          | Instructions-retired counter for RDINSTRET instruction.   |

| 0xC03  | URO       | hpmcounter3      | Performance-monitoring counter.                           |

| 0xC04  | URO       | hpmcounter4<br>: | Performance-monitoring counter.                           |

| 0xC1F  | URO       | hpmcounter31     | Performance-monitoring counter.                           |

| 0xC80  | URO       | cycleh           | Upper 32 bits of cycle, RV32 only.                        |

| 0xC81  | URO       | timeh            | Upper 32 bits of time, RV32 only.                         |

| 0xC82  | URO       | instreth         | Upper 32 bits of instret, RV32 only.                      |

| 0xC83  | URO       | hpmcounter3h     | Upper 32 bits of hpmcounter3, RV32 only.                  |

| 0xC84  | URO       | hpmcounter4h     | Upper 32 bits of hpmcounter4, RV32 only.                  |

| 0xC9F  | URO       | hpmcounter31h    | Upper 32 bits of hpmcounter31, RV32 only.                 |

Table 5. Currently allocated RISC-V supervisor-level CSR addresses.

| rable of carrently allocated K156 V supervisor level core addresses. |                                 |                                                  |                                                                                                                                                                           |  |  |  |  |  |  |  |

|----------------------------------------------------------------------|---------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Number                                                               | Privilege                       | Name                                             | Description                                                                                                                                                               |  |  |  |  |  |  |  |

|                                                                      | Supervisor Trap Setup           |                                                  |                                                                                                                                                                           |  |  |  |  |  |  |  |

| 0x100<br>0x104<br>0x105<br>0x106                                     | SRW<br>SRW<br>SRW               | sstatus<br>sie<br>stvec<br>scounteren            | Supervisor status register. Supervisor interrupt-enable register. Supervisor trap handler base address. Supervisor counter enable.                                        |  |  |  |  |  |  |  |

|                                                                      |                                 | Supe                                             | rvisor Configuration                                                                                                                                                      |  |  |  |  |  |  |  |

| 0x10A                                                                | SRW                             | senvcfg                                          | Supervisor environment configuration register.                                                                                                                            |  |  |  |  |  |  |  |

| Supervisor Counter Setup                                             |                                 |                                                  |                                                                                                                                                                           |  |  |  |  |  |  |  |

| 0x120 SRW scountinhibit Supervisor counter-inhibit register.         |                                 |                                                  |                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                                                      |                                 | Supe                                             | rvisor Trap Handling                                                                                                                                                      |  |  |  |  |  |  |  |

| 0x140<br>0x141<br>0x142<br>0x143<br>0x144<br>0xDA0                   | SRW<br>SRW<br>SRW<br>SRW<br>SRW | sscratch sepc scause stval sip scountovf         | Supervisor scratch register. Supervisor exception program counter. Supervisor trap cause. Supervisor trap value. Supervisor interrupt pending. Supervisor count overflow. |  |  |  |  |  |  |  |

|                                                                      |                                 | Supervisor                                       | Protection and Translation                                                                                                                                                |  |  |  |  |  |  |  |

| 0x180                                                                | SRW                             | satp                                             | Supervisor address translation and protection.                                                                                                                            |  |  |  |  |  |  |  |

|                                                                      |                                 | Deb                                              | ug/Trace Registers                                                                                                                                                        |  |  |  |  |  |  |  |

| 0x5A8                                                                | SRW                             | scontext                                         | Supervisor-mode context register.                                                                                                                                         |  |  |  |  |  |  |  |

|                                                                      |                                 | Superviso                                        | or State Enable Registers                                                                                                                                                 |  |  |  |  |  |  |  |

| 0x10C<br>0x10D<br>0x10E<br>0x10F                                     | SRW<br>SRW<br>SRW<br>SRW        | sstateen0<br>sstateen1<br>sstateen2<br>sstateen3 | Supervisor State Enable 0 Register. Supervisor State Enable 1 Register. Supervisor State Enable 2 Register. Supervisor State Enable 3 Register.                           |  |  |  |  |  |  |  |

Table 6. Currently allocated RISC-V hypervisor and VS CSR addresses.

| Number                                                                        | Privilege                       | Name                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                               |                                 |                                                                                                          | Hypervisor Trap Setup                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 0x600<br>0x602<br>0x603<br>0x604<br>0x606<br>0x607                            | HRW HRW HRW HRW HRW HRW         | hstatus<br>hedeleg<br>hideleg<br>hie<br>hcounteren<br>hgeie<br>hedelegh                                  | Hypervisor status register. Hypervisor exception delegation register. Hypervisor interrupt delegation register. Hypervisor interrupt-enable register. Hypervisor counter enable. Hypervisor guest external interrupt-enable register. Upper 32 bits of hedeleg, RV32 only.                                                                                                                                      |  |  |  |  |  |  |

|                                                                               |                                 |                                                                                                          | Hypervisor Trap Handling                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 0x643<br>0x644<br>0x645<br>0x64A<br>0xE12                                     | HRW<br>HRW<br>HRW<br>HRO        | htval<br>hip<br>hvip<br>htinst<br>hgeip                                                                  | Hypervisor trap value. Hypervisor interrupt pending. Hypervisor virtual interrupt pending. Hypervisor trap instruction (transformed). Hypervisor guest external interrupt pending.                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                                                                               |                                 |                                                                                                          | Hypervisor Configuration                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| 0x60A<br>0x61A                                                                | HRW<br>HRM                      | henvcfg<br>henvcfgh                                                                                      | Hypervisor environment configuration register. Upper 32 bits of henvcfg, RV32 only.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|                                                                               |                                 | ŀ                                                                                                        | Hypervisor Protection and Translation                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

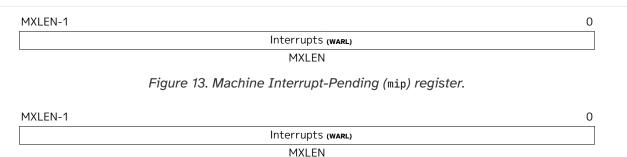

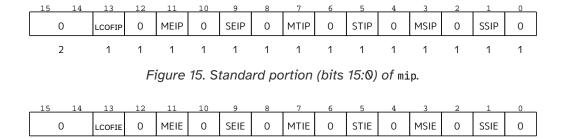

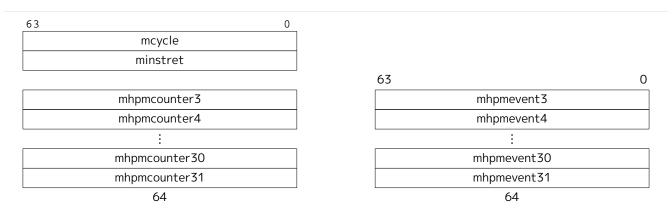

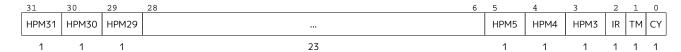

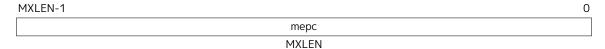

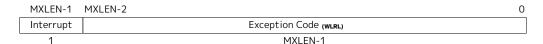

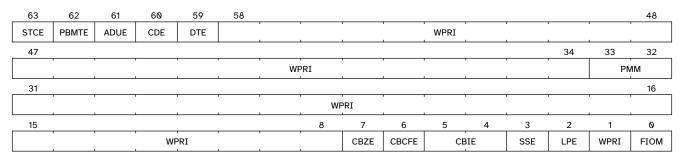

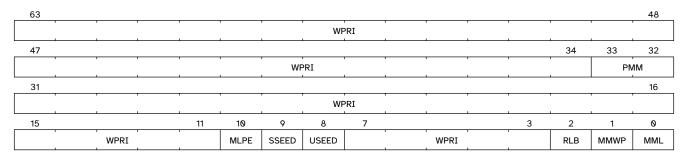

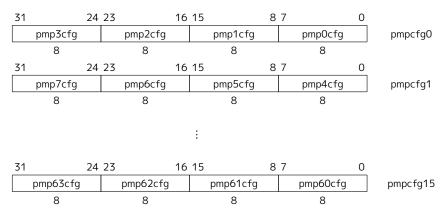

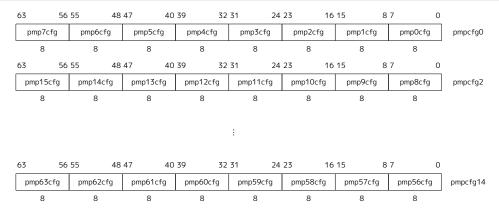

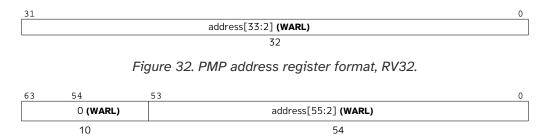

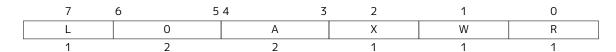

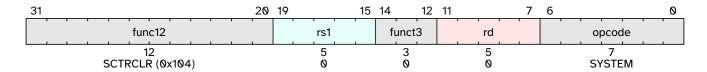

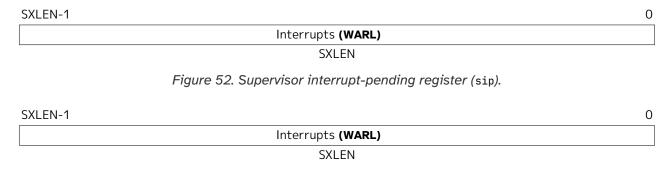

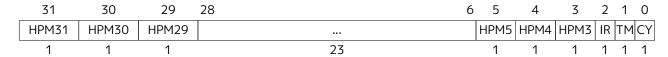

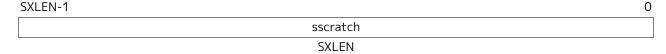

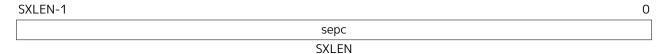

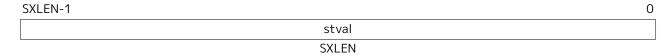

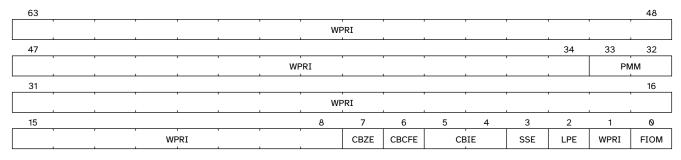

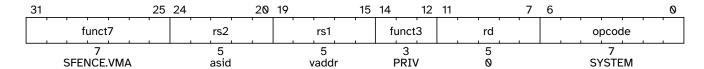

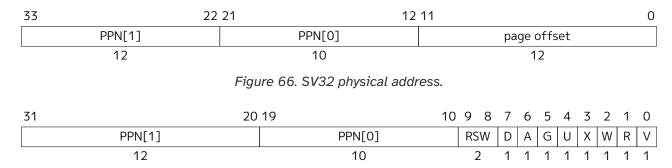

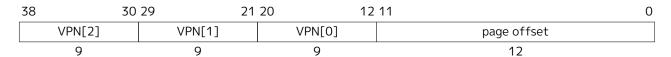

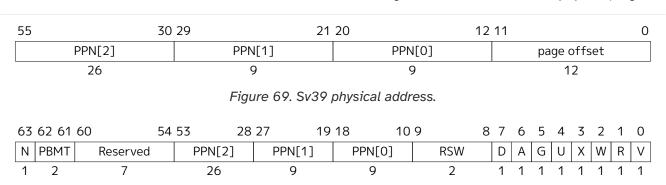

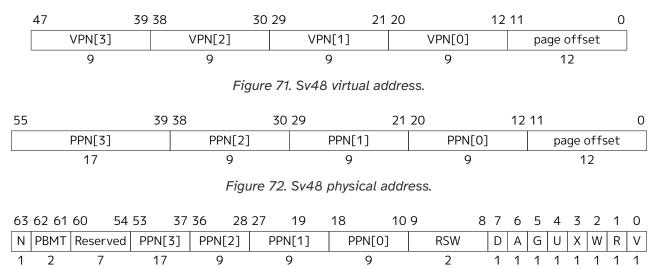

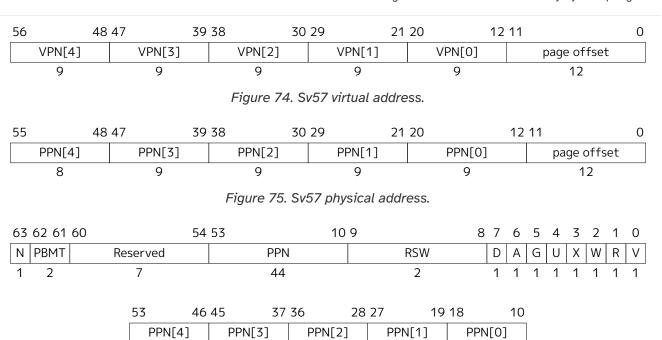

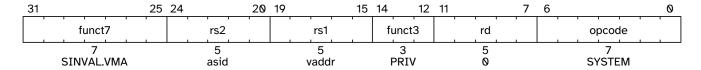

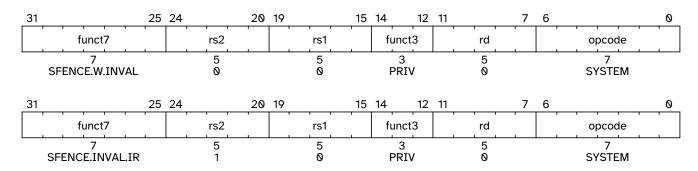

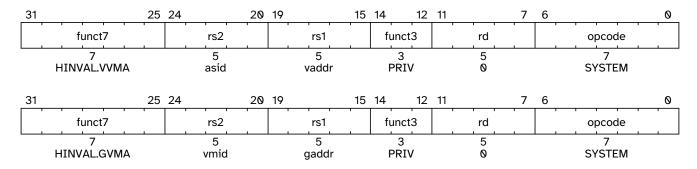

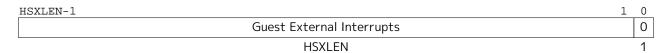

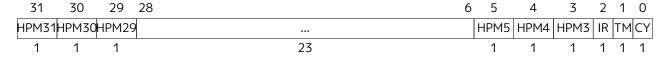

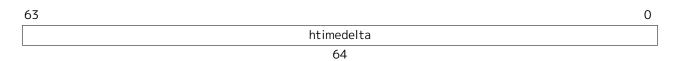

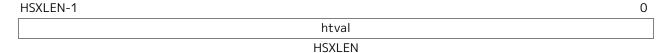

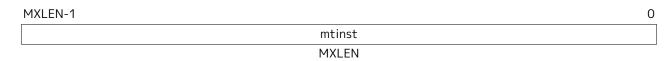

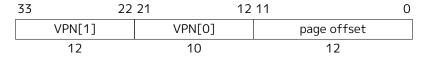

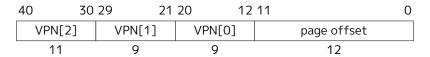

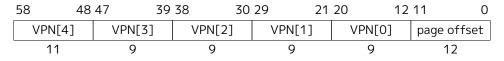

| 0x680                                                                         | HRW                             | hgatp                                                                                                    | Hypervisor guest address translation and protection.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |